# **Qualified Electronics For Low Temperature Environments**

**Principal Investigator: Jean Yang-Scharlotta (514)**

Co-Investigators: Mohammad Ashtijou (334), Michael Han (514), Wilson Parker (514), Linda Del Castillo (514), Armian Hanelli (514), Daniel Costanzo (Intern), William Norton (UT), Ziming Wang (UT), Benjamin Blalock (UT) **Program: Strategic Initiative**

| <b>Project Objective:</b><br>Commercial off-the-shelf (COTS) electronics tend to have<br>hidden margins enabling them to operate beyond datasheet<br>limits. However, very little characterization & reliability results<br>are available. Our objectives are to: | <b>Benefits to NASA and JPL (or significance of results):</b><br>Many high value targets in the solar system require exposing the spacecraft to extremely low temperature environments, but current spacecraft architecture for such extreme environments rely on central warm boxes requiring significant routing cabling which increase complexity and weight. Alternatively, there exists very few electronics specifically designed for extreme cold operation. Therefore, this R&TD task was conceived as a pathfinder for the identification and qualification of commercial components for extreme cold environments (-55C to -185C) to support future NASA and JPL missions. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>Develop a method for characterization and modeling of<br/>performance &amp; reliability for COTS in extreme cold</li> </ol>                                                                                                                              | Upon completion of the three stated objectives, we would have developed, demonstrated and provided hardware evidence of an electronic subsystem assembly capable of functioning at extreme cold environments built from selected COTS components.<br>Additionally, we would have created infrastructures upon which additional electronics can be pre-selected to be qualified for operation in                                                                                                                                                                                                                                                                                      |

| environments (-55C to -185C) of interest such as Europa,<br>Titan, Mars nights, & Lunar nights<br>2. Establish a library of candidate parts, based on their                                                                                                       | such environments.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

- characterization, literature data and technology.

- Demonstrate the methodology by building and testing a 3. cold functional assembly of cold-capable COTS selected based on technology info and characterization data.

## **Problem Statement**

Current spacecraft architecture utilizes one or more central electronics box which require significant cabling increasing complexity and weight as demonstrated by this picture of the MER rover electronics at thermal-vac testing.

Cold capable electronic can enable electronics to be distributed on the extremities of the spacecraft next to sensors and motors, but currently there exists very few electronics components designed to operate in extremely cold temperatures.

# **Key Deliverables**

## **FY 17:**

- Demo subsystem selected for building with cold capable COTS

- Technology/literature analysis to identify key candidates

- $\succ$  Check out testing to narrow down candidates completed

#### **FY19 Results:**

- > In preparation for building a full cold operation capable subsystem, we completed 24 hour sustained cold operation tests at -180C for the COTS parts needed in the full-board design, demonstrating their cold operational capabilities. For each part number, at least three parts were tested to establish statistical variation and demonstrate capability.

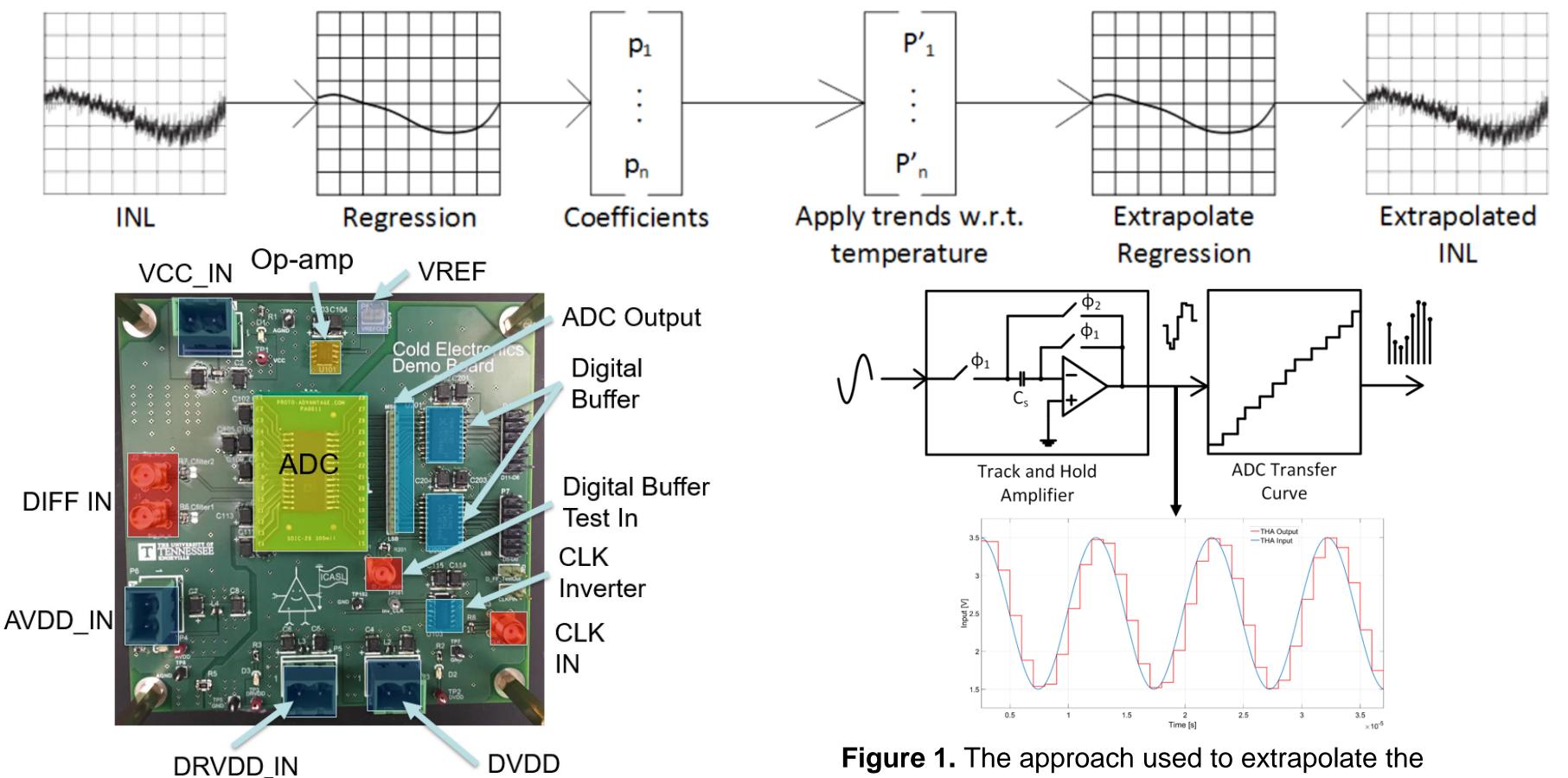

- > The universal behavior/macro-model of CMOS Nyquist-rate analog to digital converters was refined using new test data with 24 hour dwell.

- > ADC model's track-and-hold and quantization block diagrams were created in Matlab, separating the analog and digital components of the model. The model can be run by utilizing only datasheet information with minimal effort. An INL curve extraction tool is also provided.

- > Final demo board assembled from the COTS-capable parts was tested at -180C. Final revision improved system performance, including noise and signal integrity. Board behavior was monitored to compare to RT results. Overall, the assembly performed well in cold, with all the critical ADC parameters staying within 0.5% of their room temperature values. Digital currents varied more than analog ones but everything remained operational throughout.

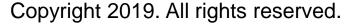

- > A Wiki page was created for cold-tested part types, including FPGAs, op-amps, ADCs, discretes, passives and others, with downloadable resources from papers, publications and presentations hosted on the site. These parts were tested at NASA centers, universities and other related institutions. Wiki access link: https://wiki.jpl.nasa.gov/display/parts/Cold-Tested+Parts+Library+and+Resources

Initial development of behavior model for an example ADC part

## **FY18:**

- > 24 hour dwell test for candidate parts to demonstrate cold operability

- ➢ Refinement of initial ADC behavioral model with 24 hour dwell test data to enhance predictive capability and extending to second ADC

### **FY19:**

- Complete 24 hour dwell test for remainder components

- >Build pathfinder subsystem utilizing cold capable components

- > Demonstrate cold operability for the pathfinder subsystem in the extreme cold environment.

- Complete cold-capable technology/parts preselection guideline with library of parts with literature data

- Complete universal ADC model for cold temperatures demonstrated on multiple ADCs of various architectures

**National Aeronautics and Space Administration** Jet Propulsion Laboratory

Figure 2. Final Demo Board Overview. Current revision improved the performance of the system, including noise and signal integrity.

transfer curve from the datasheet (top). Two main components of model: THA parameters estimated, then INL curve for the transfer function is found.

|   | Part Type            | Part Number   | Type/Technology                                             | Test Type | Lowest<br>Test<br>Temp.<br>(°C) | # of<br>Parts<br>Tested | Test<br>Institution | Resource Title                                                                                                            | Resource Document                                                                                         | Comments                                                                                                     |

|---|----------------------|---------------|-------------------------------------------------------------|-----------|---------------------------------|-------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 1 | DC-DC                | 1003S12HN     | 10W Single Output<br>Power Supply Module<br>DC/DC Converter | Static    | -180                            | 1                       | NASA GRC            | Evaluation of COTS<br>SiGe, SOI, & Mixed<br>Signal Electronic<br>Parts for Extreme<br>Temperature Use in<br>NASA Missions | 0930 - Reliability of SiGe, SOI, and<br>Advanced Mixed Signal Devices for<br>Cryogenic Space Missions.pdf | Oscillations in input<br>current at -140°C<br>under heavy loading.                                           |

| 2 | Voltage Regulator    | 1003S12HN     | Buck                                                        | Dynamic   | -180                            | 1                       | See paper           | COTS IC Parts Pre-<br>Selection Guideline<br>for cryogenic<br>applications                                                | coldguideline-part2-rev2-0924.docx                                                                        | Oscillation in input<br>current observed at<br>133 K under heavy<br>loading.                                 |

| 3 | Passive<br>Component | 200B104KT50XT | BX Ceramic<br>Capacitors                                    | Dynamic   | -185                            | 3                       | NASA JPL            | Reliability Final<br>Report for Passive<br>Components, ADC,<br>FPGA: Cryogenic<br>Testing                                 | ArmianHanelli_FinalReport.pdf                                                                             | This capacitor<br>performed the worst<br>with value drops of<br>about 70% and is not<br>recommended for use. |

Figure 3. A sample of the Wiki page showing 3 part types, related information and resources.

PI/Task Mgr. Contact Info: Jean.Yang-Scharlotta@jpl.nasa.gov

#### **FY19** Publications

Will Norton, Ziming Wang, Benjamin J Blalock, Jean Yang-Scharlotta, Mireyong Song, Mohammad Ashtijou, and Mohammad [A] Mojarradi, "Modeling of Select Mixed-Signal Electronics for Cold

Temperature Environments," Proceedings of IEEE Aerospace Conference 2019.

Will Norton, Ziming Wang, Benjamin J Blalock, Jean Yang-Scharlotta, Mireyong Song, Mohammad Ashtijou, and Mohammad

[B]

Mojarradi, "Testing and Modeling of a SAR ADC for Cryogenic Applications," *Proceedings of 2019 IEEE International Midwest Symposium on*

Circuits and Systems.

Acknowledgements: We gratefully acknowledge the guidance and support of task lead Dr. Mohammad Mojarradi and task sponsor Dr. Harald

Schone. We also thank the contribution of past interns Thomas Peev, Bianca Rhym, Haolin Yang, Arad Saebi, Aminah Wright, & Roy Tan.