# Ka-Band GaN-Based Solid-State Power Amplifier for Deep-Space Telecommunications

## Principal Investigator: Masatoshi Kobayashi (337); Co-Investigators: Salman Haque (337), Sushians Rahimizadeh (333), Scot Stride (337), Mark Taylor (333)

### **Program: FY21 R&TD Strategic Initiative**

## **Objectives:**

The objective of this research is to investigate the path towards achieving a highly efficient Ka-band (31.8 to 32.3 GHz) solid-state power amplifier for deep-space telecommunications applications.

Develop a 5-Watt power amplifier with > 40% poweradded efficiency (used with the 40 dBi gain from the Kaband Parabolic Deployable Antenna can provide approximately 100 bps of telemetry downlink to the DSN at a range of 10 Astronomical Units).

Develop a spatial combiner for increased output power. Such amplifiers can not only compete with traditional TWTAs, but may prove advantageous considering the inherent delicate nature, the technical expertise required, and the size/volume required for TWTAs.

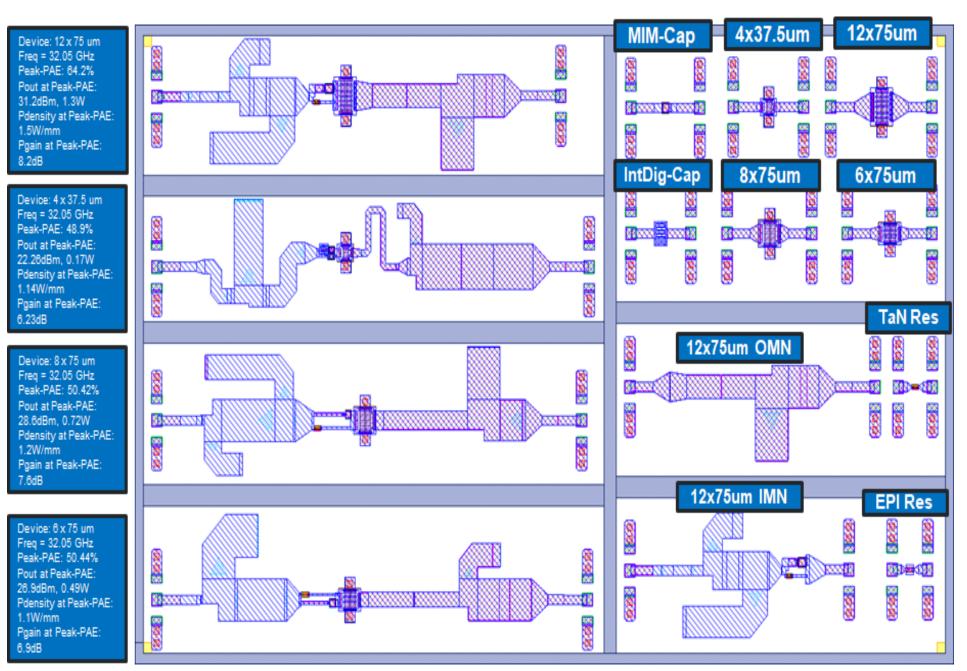

Figure 1. HRL GaN/SiC 40-nm test coupon with harmonicmatched 4, 6, 8, and 12 fingered transistors. Coupon is useful to JPL/NASA for study across Ka-band and multiple bands.

∰ 25 –

g 20

National Aeronautics and Space Administration

Jet Propulsion Laboratory California Institute of Technology Pasadena, California

### www.nasa.gov

### Acknowledgements:

Mr. Raymond Quintero and Mr. Steven Montanez for their design and assembly support.

Dr. Dimitrios Antsos for continued advisory role along the research task. Dr. Steven Townes, Dr. Joseph Lazio, and Dr. Rebecca Castano for the funding and opportunity.

Nick Chopra of ReconRF Inc. for the MMIC development and loadpull measurements.

Strategic Focus Area: Advancing Solar System Exploration with Telecommunications Links

## Approach and Results:

Access to model PDK's from 9 foundries and each technology was simulated for maximum PAE. The resulting top performers identified were both domestic and international: HRL (40-nm GaN/SiC), OMMIC (60-nm GaN/Si), Cree (150-nm GaN/SiC), and WIN (150-nm GaN/SiC).

HRL: Design a test coupon with 2<sup>nd</sup> harmonic structures. Include ability to measure for multiple bands. Partner with ReconRF to complete this task. (Figure 1)

PDK based simulations for OMMIC's 60-nm GaN/Si process and WIN's 150-nm GaN/SiC indicated PAE in the 50%-60% range with 1 W output under both fundamental and harmonic matching. Measure coupons to verify performance (Figure 2).

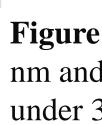

The building block from last year's 2.6 W Cree G28v5 150-nm GaN/SiC based design was revisited. ReconRF load pulled the 6x50 um device at 30 V operation with tuning at fundamental only and an output power of 1.1 W at 53% PAE was observed. Using the same 2 mm x 3 mm area, transistor count doubled for increased output power of 4.4 W with a PAE of 40% and is planned for MPW fabrication next year.

• In addition to power MMIC work, Qorvo QPA2225D and OMMIC CGY2250UH devices offer PAE below 9% when driven at 0 dBm (1 mW) and are not useful as drivers in an SSPA with an overall PAE of 40%. A custom driver MMIC is being designed.

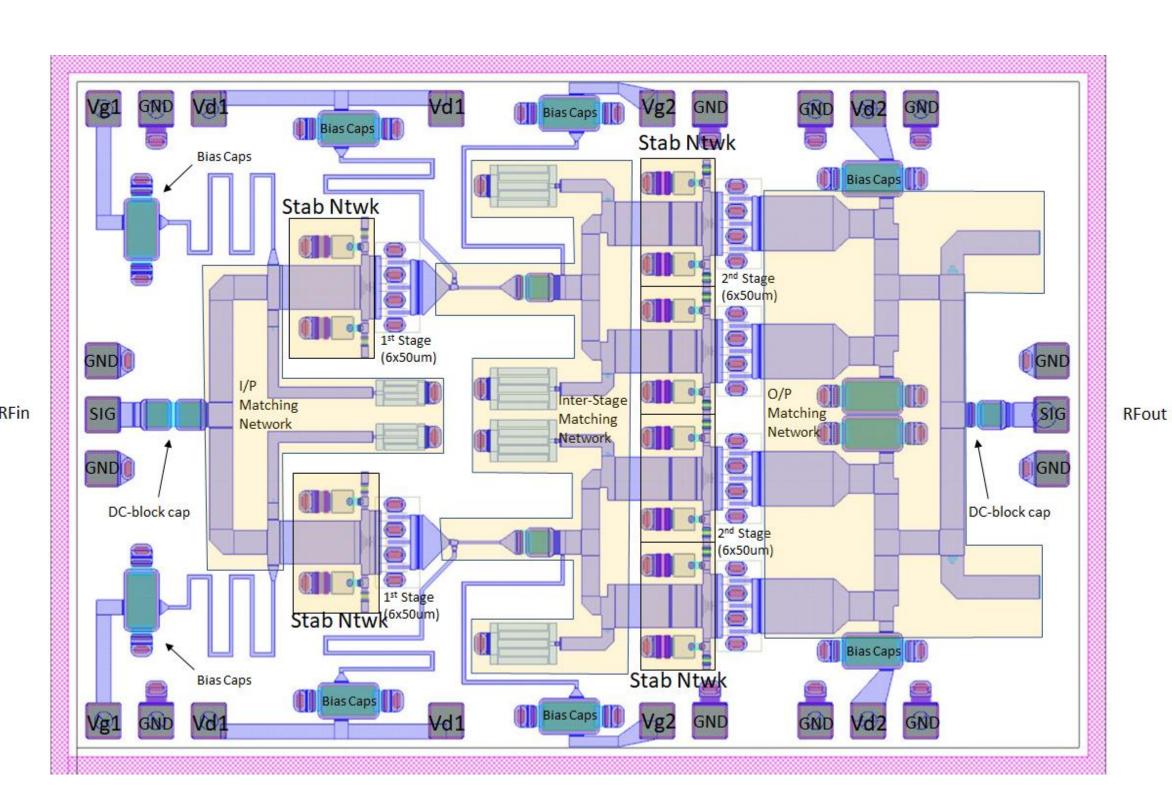

A survey of commercial offerings for packaging GaN devices identified the StratEdge SE50 package. Ten completed packages of 5 W die and a test fixture with an associated power board have been designed to test the packaged devices and characterize the package's performance (Figure 4).

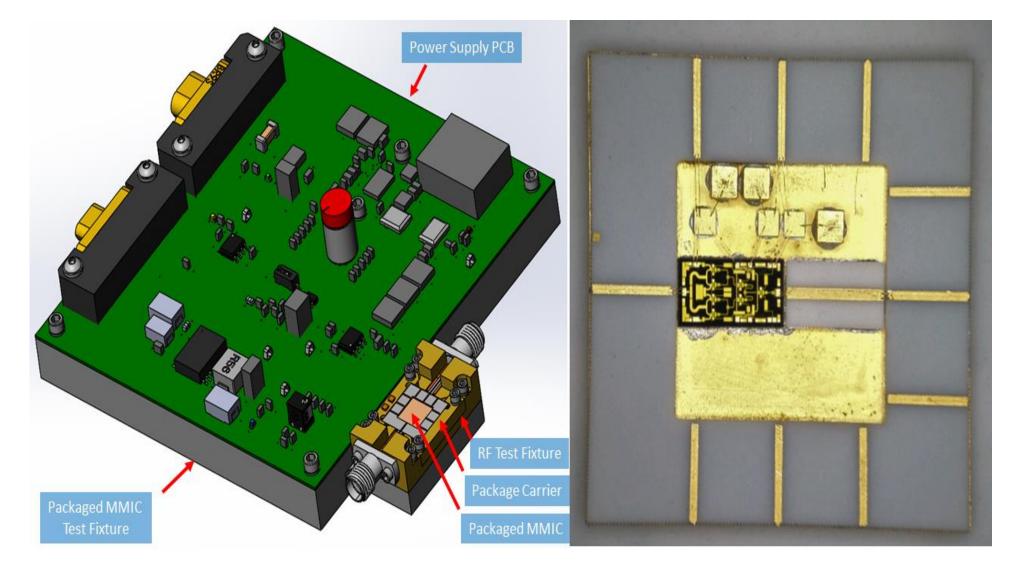

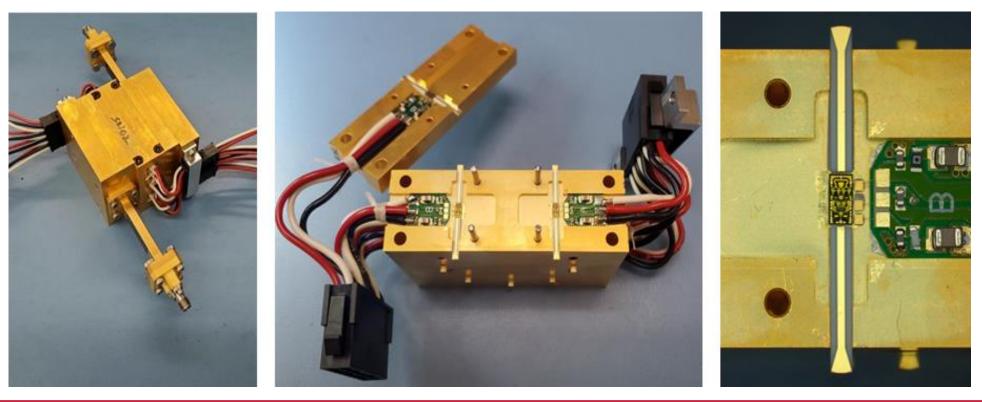

The 8-way SPCA was outfitted with thru lines to make passive measurements, tuned, and output combined) at 32 GHz. The passive thru lines were removed and replaced with active devices (TGA2594 die) and made ready for small signal characterization with large signal to follow (Figure 5).

Figure 2. PAE and output power measurements for OMMIC 60nm and 100-nm GaN/Si (top) and WIN 150-nm GaN/SiC (bottom) under 32 GHz (fundamental frequency) source/load pull only.

**Figure 3.** Completed layout for a two-stage, 2:4 architecture, high efficiency power amplifier MMIC designed on Cree's 150-nm GaN/SiC G28V5 process.

## Significance of Results/Benefits to NASA/JPL:

SiC is the most prevalent substrate used for GaN due to good thermal conduction. Thermal effects were observed during characterization of OMMIC's GaN/Si. GaN/Si may be useful in low power driver amplifier design and this is being investigated. Without availability of high gamma harmonic tuning stations for Kaband, JPL and ReconRF designed the second harmonic structures around HRL transistors within the HRL test coupons. Available low gamma harmonic tuning stations can be used to measure and adjust the impedance to maximum PAE. This approach may facilitate high frequency design for all future OMMIC, WIN, etc JPL designs as well.

Without harmonic tuning, a Cree 6x50 um device was measured at 53% PAE at 30 V. A 4.4 W power MMIC was designed around this operation with layout passing DRC. These MMICs may need packaging for flight and StratEdge was able to provide JPL a GaN packaging solution along with assembly – providing a path for all future GaN packaging. With the anticipation of high efficiency 5 W MMICs being produced, a novel 8-way spatial combiner has been designed and populated with commercial, TGA2594, 5 W MMICs and could produce >30 W. Assembly has completed and characterization has begun.

Figure 4. 3D model of test fixture for packaged StratEdge SE-50 (left) and a de-lidded SE-50 package with a TGA2594 MMIC, 50 ohm microstrip line, and passives (right).

Figure 5. SPCA fully assembled (left) de-stacked (center) and closeup of TGA2594 hybrid with waveguide to microstrip transitions and bias board show (right).